## Brandenburgische Technische Universität Cottbus

Fakultät Informatik

# Evaluation of Design Alternatives for Flexible Elliptic Curve Hardware Accelerators

Diplomarbeit zur Erlangung des akademischen Grades Diplom-Informatiker

| Bearbeiter:       | Steffen Peter                          |  |  |

|-------------------|----------------------------------------|--|--|

|                   | Matrikelnummer: 9802986                |  |  |

| Gutachter:        | Prof. DrIng. Rolf Kraemer              |  |  |

|                   | Prof. DrIng. Heinrich Theodor Vierhaus |  |  |

| Betreuer:         | Dr. Peter Langendörfer                 |  |  |

| Bearbeitungszeit: | 28.08.2005 - 22.02.2006                |  |  |

# Erklärung

Hiermit versichere ich, die vorliegende Arbeit selbständig und ohne Benutzung anderer als der von mir angegebenen Quellen angefertigt zu haben. Alle aus fremden Quellen direkt oder indirekt übernommenen Gedanken sind als solche gekennzeichnet. Die Arbeit wurde noch keiner Prüfungsbehörde in gleicher oder ähnlicher Form vorgelegt.

Frankfurt(Oder), den 22. Februar 2006

\_\_\_\_\_

# Contents

| 1. | Introduction                          | 1  |

|----|---------------------------------------|----|

| 2. | Cryptography                          | 5  |

|    | 2.1. Cryptography basics              | 5  |

|    | 2.2. Public key cryptography          | 9  |

| 3. | Finite fields                         | 17 |

|    | 3.1. Finite fields basics             | 17 |

|    | 3.2. Polynomial multiplication        | 21 |

|    | 3.3. Polynomial squaring              | 31 |

|    | 3.4. Reduction                        | 32 |

|    | 3.5. Modular multiplicative inversion | 37 |

| 4. | Elliptic curve cryptography           | 45 |

|    | 4.1. ECC operations                   | 46 |

|    | 4.2. EC point multiplication          | 49 |

| 5. | Hardware designs for ECC              | 53 |

|    | 5.1. Hardware development work flow   | 53 |

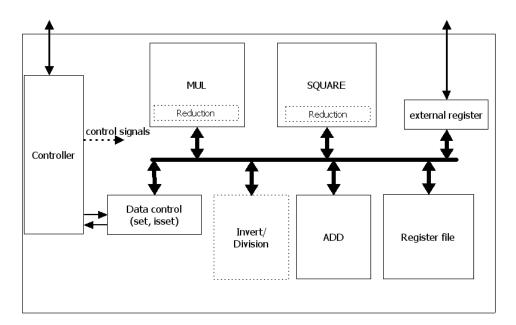

|    | 5.2. Processor architecture           | 54 |

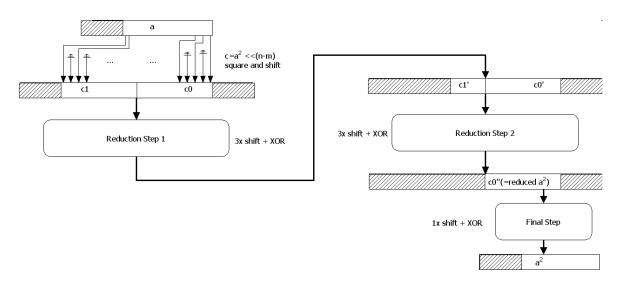

|    | 5.3. Reduction                        | 61 |

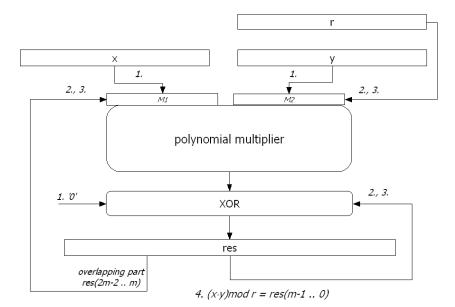

|    | 5.4. Polynomial multiplication        | 62 |

|    | 5.5. Polynomial squaring              | 72 |

|    | 5.6. Modular multiplicative inversion | 74 |

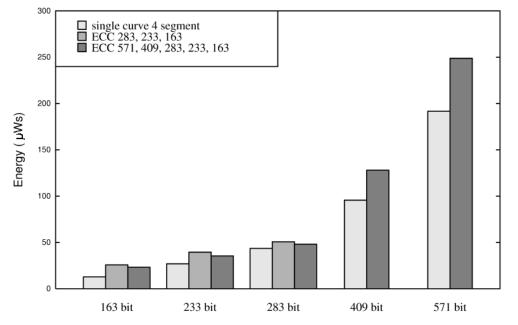

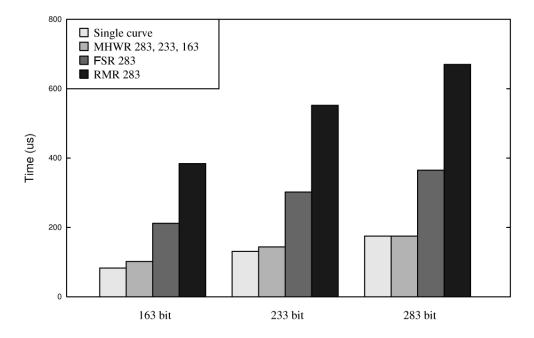

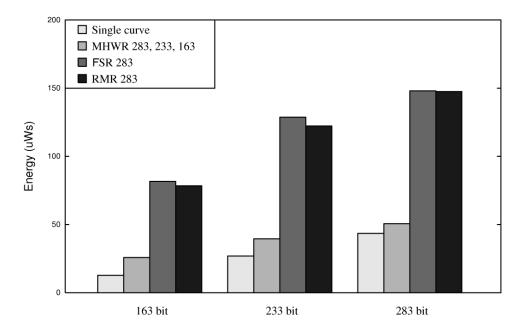

| 6. | Efficient hardware designs for ECPM   | 79 |

|    | 6.1. EC point multiplication          | 79 |

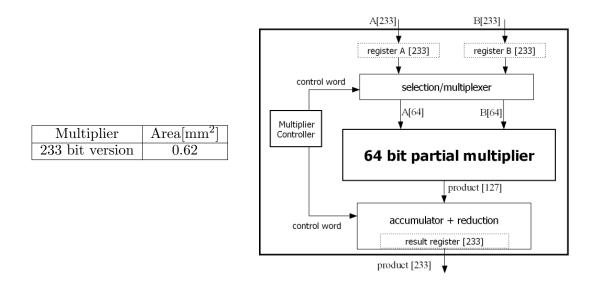

|    | 6.2. Design of a ECC 233 coprocessor  | 86 |

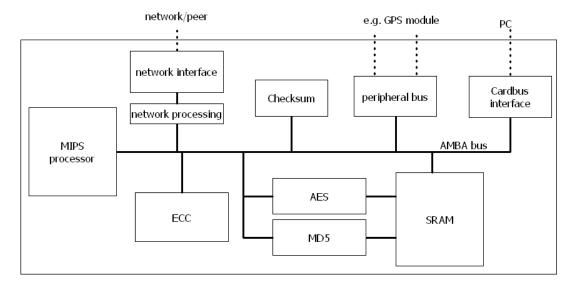

|    | 6.3. Integration in a system on chip  | 92 |

|    | 6.4. Conclusions                      | 95 |

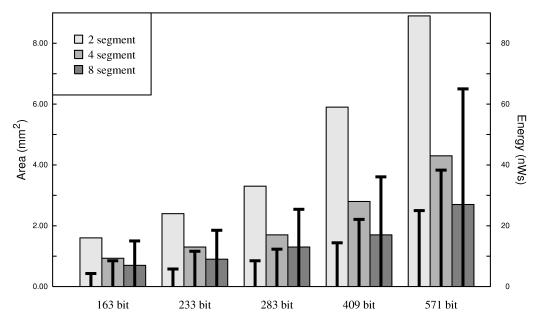

| 7. | Flexible hardware designs for ECC     | 99  |

|----|---------------------------------------|-----|

|    | 7.1. Flexibility                      | 99  |

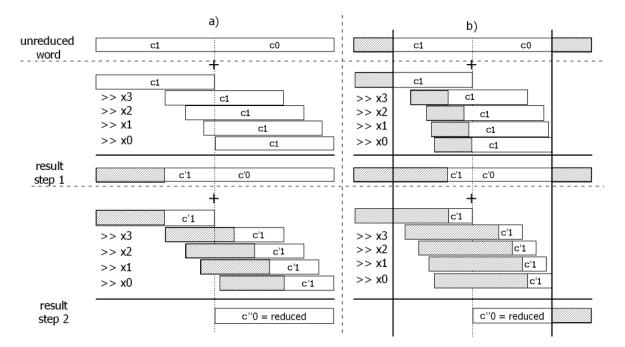

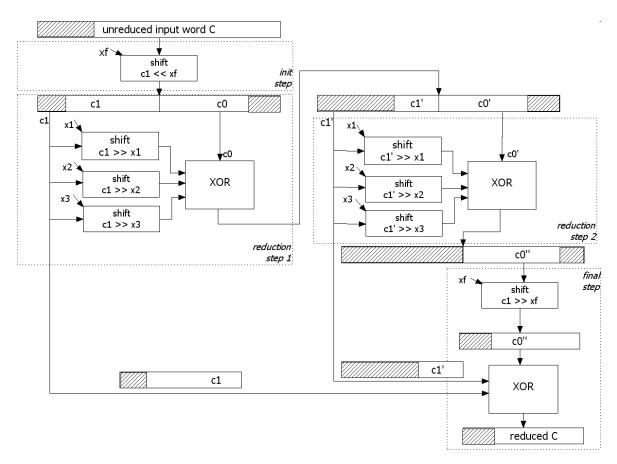

|    | 7.2. Reduction                        | 103 |

|    | 7.3. Polynomial multiplication        | 109 |

|    | 7.4. Polynomial squaring              | 113 |

|    | 7.5. Modular multiplicative inversion | 115 |

|    | 7.6. Flexible ECC designs             | 115 |

| 8. | Conclusions                           | 123 |

| Α. | Used abbreviations                    | 133 |

vi

# 1. Introduction

Amid growing demand for mobile communication and business over networks such as the Internet, data protection and authentication are an inevitable need. With the rapid migration to wireless solutions, eavesdropping becomes ever easier and the security issues become more urgent. Cryptographic approaches have properties that provide the fundamentals for secure communication.

For a long time most cryptographic applications had been performed by symmetric key methods. Symmetric key cryptography entails all cryptographic methods that perform the decryption step with the same key as the encryption. The cryptographic algorithms are secure and fast, but they do not provide answers for important issues concerning communication over insecure channels:

- How to send an encrypted message when there is no secure way of key exchange?

- How to authenticate the origin of a digital message to a third party, an equivalent to the handwritten signature?

In 1976 Whitfield Diffie and Martin Hellman introduced an asymmetric key approach [3], which is known as public key cryptography. Hereby, the encryption and decryption steps are performed with different keys. A message that was encrypted with one key can only decrypted by a different associated key. When one key is kept secret, which is the private key, and the other one, the public key, is published openly, there are a lot of applications that can satisfy the security needs. Public key cryptography allows everyone to encrypt messages with a public key that only the person with the private key can decrypt - an idea that solves the key exchange problem. The signature issue is solved when only the owner of the private key is able to encrypt a message that everyone can decrypt with a corresponding public key.

A public key method that has become the most popular public key approach is the RSA algorithm [42], which was presented in 1978 by and named after the three developers Ron Rivest, Adi Shamir and Len Adleman. Seven years later, Neal Koblitz[22] and Victor Miller[30] independently proposed elliptic curve cryptography (ECC) as a specific algorithm for public key cryptography. Indeed, ECC achieves the same level of cryptographic strength as RSA by much shorter key lengths. These shorter key lengths improve the feasibility of public key

cryptography in mobile devices substantially, since they not only imply less bandwidth usage but also a reduction of memory and processing efforts. This is important since all secure public key approaches are connected with a very high operating expense.

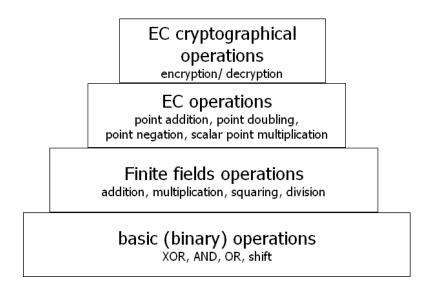

Despite the short key lengths and the corresponding less computing efforts, the calculation of an ECC operation is still extremely extensive and involved. Especially on low powered mobile devices such as sensor networks or on RFID chips, the application of ECC is still an issue. Software implementations that are running on such systems require several seconds and hence a huge amount of energy for a single ECC operation.

In the last years a number of hardware accelerators for ECC operations have been proposed that improve the performance and the reduce energy consumption by orders of magnitude. Hereby, the emphasis was mostly placed on fast but tailored designs for a selected elliptic curve. The limitation to a single elliptic curve may be problematic, particularly with regard to ASICs, which are supposed to be used for years. Changed protocols and standards may cause the need for adaptations of the used curve as can also happen due to uncovered vulnerabilities in the cryptoanalysis. This is why in this work not only efficient hardware designs for a single curve implementation are investigated but also designs that can realize flexible ECC accelerators.

The primary goal of this diploma thesis is therefore the investigation of approaches for flexible and modular architectures of ECC hardware accelerators. This is preceded by extensive studies of existing methods to find suitable techniques and to identify potential problem areas. The theoretical considerations should result in efficient algorithms for the required operations. Special emphasis will be placed on investigations concerning efficient polynomial multiplications, which represent the most expensive base operation of ECC. The results of this investigations will lead to the development of new hardware designs to satisfy the requirements, such as execution time, area, and energy consumption. An efficient single curve implementation should prove the correctness of the considered algorithms and provide comparable data such as speed and size. Even though the primary focus is placed on an ASIC, an FPGA implementation should supply functional verification. Furthermore, the concept should be confirmed as the ECC design will be part of a real communication system on chip. The single curve ECC design is the basis for flexible ECC accelerators.

The rest of this thesis is organized as follows:

In Chapter 2 the cryptographic ideas, which were briefly mentioned in this introduction, are further presented and the benefits of ECC are demonstrated.

Chapter 3 introduces the finite fields that are the base fields of the elliptic curves. Since operations on these field are the functional backbone of ECC, they are comprehensively explained and alternative fast algorithms are described and compared. Special attention is given to the multiplication operation. Based on known approaches an improved multiplication is devised that decreases the complexity of the operation in implementations considered later. In Chapter 4 the operations on the elliptic curve are described. The algorithms for these operations, in particular the scalar point multiplication, provided there, are determined to be implemented in hardware later.

Chapter 5 applies the algorithms of Chapter 3 and 4 and presents efficient hardware implementations of the main operations required for an efficient ECC design. Also a fundamental architecture of the considered hardware design in presented.

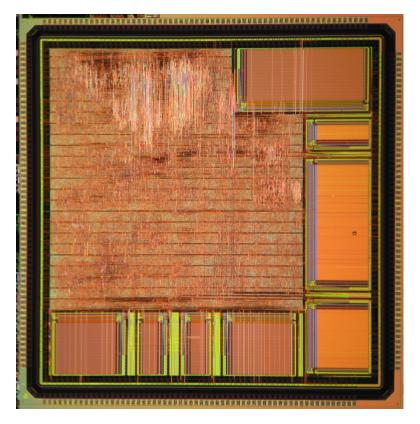

Chapter 6 assembles the separate hardware blocks of the previous chapter to an efficient single curve ECC processor. For this, the design space for ECC hardware designs is explored. Eventually, the ECC design will be embedded into a system on chip, which is really made in silicon.

In Chapter 7 the existing ECC design will be extended to a flexible ECC accelerator. Therefore, different approaches of realizing the flexibility are discussed. The main focus is hereby placed on flexible reduction methods in the base field. Finally, the extensive considerations of the preceding chapters will lead to efficient flexible designs for the acceleration of ECC.

# 2. Cryptography

This chapter provides cryptographic basics and algorithms. The main focus is placed on the introduction of different approaches of the public key cryptography. The advantage of ECC over other cryptographic approaches is demonstrated by comparing the efforts for breaking the cryptographic systems.

## 2.1. Cryptography basics

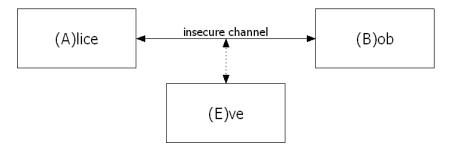

Cryptography (from Greek kryptós, "hidden", and gráphein, "to write") is the technique of converting information into and from a format that is unreadable without secret knowledge. A classical application of cryptography in computer science is the communication over an unsecured channel. Traditionally, an entity A, named Alice, and an entity B, named Bob, communicate over this insecure channel. An insecure channel is every communication channel where it is possible for an entity E, a villain named Eve, to interfere with the communication. Possible interferences can be eavesdropping, but also a changing, delaying, dropping or emitting of packets. This compromises the security of the communication.

*Figure 2.1.:* The standard communication scenario: Alice and Bob want to communicate over an insecure channel. A third person Eve is able to eavesdrop and to modify elements of the transaction.

Desired properties of a secure communication channel are [48],[47]:

- **Confidentiality:** When Alice sends a message to Bob, protection against unauthorized disclosure of the data to Eve should be provided.

- **Data integrity:** It should be guaranteed that the sent data is protected against unauthorized or unintentional modifications. For example, Eve should not be able to intercept and modify data.

- Authenticity: The identity claimed by or for a system entity must be verifiable. When Bob communicates with Alice, he must be sure that it is really Alice at the other end.

- **Non-repudiation** The origin of a message must be verifiable and can be used as a proof. When Bob receives a message from Alice, she cannot deny having sent it.

Cryptography provides the tools to obtain these properties. Confidentiality is attained when plain a message is converted into an unreadable form and a reconversion is only possible with hidden secret informations. Data integrity can be assured by generating a hash value over the content. When the content changes, intentionally or unintentionally, it does not match the hash value.

Authenticity can be obtained by digital signatures or challenge-response protocols. Both approaches are based on the correct encryption or decryption of a message with a key that is exclusively known to one person.

Non-repudiation is a combination of data integrity and authenticity. Consider he case that Bob receives a message from Alice and can be sure that the content was not changed (data integrity). When it can additionally be verified that the message was original written by Alice (authenticity), it is evidence that she sent the message, which Bob has received, and she cannot deny it.

#### 2.1.1. Hash functions

Hash functions are functions that map an input of variable length on a number of fixed bit length. This number is the hash value. These functions in particular find cryptographic application in data integrity and data authentication. It should generate a possibly unique mapping that provide the following conditions [38]:

- The input can be any length

- The length of the output of the hash function is fixed

- Computing of the function must be easy

| hash function | hash length [bit] | security strength |

|---------------|-------------------|-------------------|

| MD4           | 128               | $2^{20}$          |

| MD5           | 128               | $2^{39}[53]$      |

| SHA-1         | 160               | $2^{69}[52]$      |

| SHA-2         | up to $512$       | up to $2^{256}$   |

| WHIRLPOOL     | 512               | $2^{256}$         |

Table 2.1.: Properties of cryptographic hash functions: modern highly secure hash functions calculate a 512 bit hash value. An attack on these hash algorithms requires  $2^{256}$  attempts in average to be successful.

- The function must be 'one way' (preimage resistance). This means it should be computationally infeasible to find a message for a given hash value.

- The function should be collision resistant. This means it should be computationally infeasible to find two different messages with the same hash value.

Many different hash function have been developed in history. Well known is for example the 'Cyclic Redundancy Check' (CRC), which is mainly used for error detection in data streams or files. It is not recommended to use it to assure data integrity, since it is possible to create messages for a given hash values very efficiently. To ensure data integrity hash functions must provide a sufficient preimage and collision resistance. Hash functions that provide this properties are termed cryptographic hash functions. Popular examples of cryptographic hash functions are MD4 and MD5 [41], which calculate 128-bit hash values, and SHA-1 [6] with a 160-bit hash value. Since these hash functions have been successfully attacked ([52], [53]), stronger algorithms are recommended. Today, the SHA-2 functions [51] with hash lengths up to 512 bit and the WHIRLPOOL hash function [40] are considered as safe.

#### 2.1.2. Digital signature

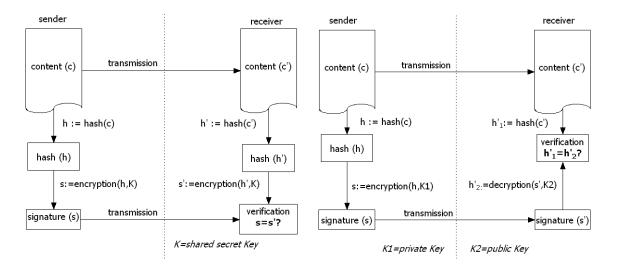

The digital signature is a method for authenticating digital information. The intention is to obtain a digital equivalent to the classic written signature on paper. It should verify that the underwriter has read and acknowledged the content. Say, Alice wants to send a message, for example an order, to Bob, and data integrity, authenticity and non-repudiation should be guaranteed. In the previous section hash functions were already described, which assure that a received message has not been changed. Indeed, it is possible for Eve to change the content and generate a new hash to pretend an original message. To eliminate this risk, for a digital signature the hash generation is followed by a second step. In this step Alice encrypts the original hash value using a key that authenticates her.

Figure 2.2.: Signature schemes realized with shared secret keys (left) and public key approaches (right). The tasks for the sender are identical in both methods: the encrypted hash value of the content is sent together with the content. The difference is on the receiver side. In the shared key approach the signature is redetermined and verified, whereby with a public key the signature is decrypted and verified against the hash of the received message.

Generally, there are two possible ways of performing this authentication:

- Both parties share one key. Alice encrypts the hash of the sent message with the same key that Bob applies to encrypt the hash of the received message. If both encryptions are identical, then it is evidence for Bob that Alice sent the text, because no one but Alice and Bob know the secret key.

- Both parties use different keys for encryption and decryption. Alice encrypts the hash value of the message with one key and sends the result together with the text. Bob can decrypt the encrypted hash with a corresponding key. To verify the received message, Bob compares the decrypted hash with the determined hash of the received message.

The shared key approach is connected with disadvantages. First, there is the problem of distributing the key. How can Alice and Bob obtain the same key without giving Eve the chance of intercepting it? In addition, this approach proves the identity of Alice to Bob but it does not prove it to a third party. This is because Bob can generate the signature himself, since he shares the same key.

The second approach where Alice has a private key and Bob uses a corresponding public key, is known as public key approach, because Bob's key can be published. Thus, everyone can verify that Alice is the origin. In addition, it is no threat when Eve intercepts the public key. One can see that the public key approach is indeed a good solution for the problem of digital signatures, mutual authentication and key exchange. This is why public key cryptography is considered thoroughly in the following.

## 2.2. Public key cryptography

The public key cryptography, which is also known as asymmetric cryptography, is a cryptographic approach with different keys for encryption and decryption. One key, the public key, can be published while the other one, the private key, is kept secret. Applying this approach, it is possible for everyone to encrypt a message with the public key and only the owner of the private key can decrypt it. As mentioned before, public key cryptography is useful for digital signatures. In this application the public can decrypt a message that must have been encrypted by the owner of the private key.

To assure security, a public key cryptographic system must have the following properties:

- It must be computationally infeasible to determine the private key from the public key.

- It is not possible to reverse the public key cryptographic operation without the associated private key.

These properties can be realized with mathematical one-way functions. These 'trapdoor' operations are performed easily in one direction whereby the calculation of the reverse operation is very expensive. Until today two mathematical principles have been applied for public key cryptography:

- Factorization

- Discrete logarithm

#### 2.2.1. Factorization problem

The multiplication of two large integers is an easy operation. The reverse operation, that is to find the factors for a given product, is far more complicated. Today no algorithm is known that solves the factorization problem in polynomial time. The first adaption of the factorization algorithm for public key cryptography is the RSA algorithm.

#### RSA

The RSA algorithm is probably the most well-known public key algorithm today. RSA stands for the initials of the surnames of the developers Ron Rivest, Adi Shamir and Len Adleman. RSA uses the fact that for specific combinations of integers d and e it is true that  $m^{ed} \equiv m \mod n$ . Thus, a message m can be encrypted with the public key tuple (d, n) by applying  $c \equiv m^d \mod n$ . The encrypted word c can be decrypted with the private key (e, n), since  $c^e \mod n = m^{d^e} \mod n = m^{de} \mod n = m$ .

The algorithm is based on the little Fermat theorem, which says that for any prime p and any integer a which is coprime to p it is valid that

$$a^{(p-1)} \equiv 1 \mod p$$

Thus it is also valid that  $a^{i(p-1)} \equiv 1 \mod p$  for any integer *i* as long as  $a^i$  is coprime to *p* Besides *p*, RSA uses another prime *q* so that finally:

$$n := pq$$

$$a^{i(q-1)} \equiv 1 \mod n$$

,  $a^{i(p-1)} \equiv 1 \mod n$  and  $a^{i(p-1)(q-1)} \equiv 1 \mod n$

Thus

$$a^{i(p-1)(q-1)+1} \equiv a \mod n$$

RSA uses this fact by selecting two integer d and e so that:

$$ed \equiv 1 \mod (p-1)(q-1)$$

with other words

$$ed = i(p-1)(q-1) + 1$$

It follows

$$a^{ed} \equiv a \mod n$$

Now (e, n) is the public key and (d, n) the private one. With these keys the following operations are defined:

Encryption:  $c \equiv m^d \mod n$

Decryption:  $m \equiv c^e \mod n$ , since  $m^{d^e} \mod n = m^{de} \mod n$

This means, both encryption and decryption are performed by raising a data word m or c to power d or e respectively modulo n. For a secure system all variables should have a size of several hundreds of bits.

To break the system one must determine e for the given tuple(d, n) so that  $de \equiv 1 \mod (p-1)(q-1)$ . For this it is necessary to find the factors p and q for the product n. With p and q it is easy to find the private key d. Thus RSA relies on the fact that factorizing very large numbers is a problem which is extremely difficult to solve.

Concretely, the most efficient method of factorizing large numbers is Number Field Sieve [36]. The expected running time of that algorithm is proportional to [23]

$$e^{(1.9229+O(1))\cdot\ln(n)^{1/3}\cdot\ln(\ln(n))^{2/3}}$$

which is subexponential when n goes to infinity.

Despite the subexponential running time, RSA can be considered as safe when the selected keys are long enough. The largest successfully broken RSA key that has been reported is a 200-digits RSA number that could be factorized in May 2005 [18]. The process of the factorization of the 663-bit number took more than one year on a cluster of 80 2.2 GHz Opterons.

#### 2.2.2. Discrete logarithm systems

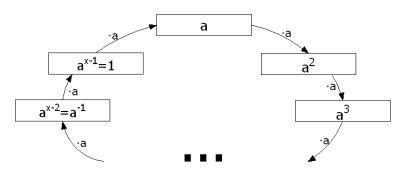

The second important public-key cryptography scheme is the group of discrete logarithm systems. These systems rely on the idea that in a multiplicative cyclic group  $\mathbb{G}$  it is very difficult to find the integer k for the given elements g and  $h \in \mathbb{G}$  so that  $h = g^k$ , while it is easy to calculate h when g and k are known.

The DL systems operate in a finite group  $(\mathbb{G}, \cdot)$ . In the simplest case  $\mathbb{G}$  is the set of integers modulo p,  $\{0, 1, 2, ..., p - 1\}$ . The operation  $\cdot$  denotes the multiplication modulo p on that group.

Selecting an element  $g \in \mathbb{G}$ , one can create a subgroup  $(\langle g \rangle, \cdot)$ , whereby the set  $\langle g \rangle = \{g^i : 0 \le i \le q-1\}$  consists all powers of g, while q is the smallest nonzero integer such that  $g^q = 1$ . This q is called the order of the subgroup. Since the subgroup was generated by g, g is called the generator of the group.

Example: For the integers modulo p = 11 one obtains the group  $\mathbb{G}$  with the members  $\{0, 1, 2, ..., 10\}$ . Now selecting one element g = 4, the multiplicative subgroup  $\langle g \rangle$  of  $\mathbb{G}$  consists of the members  $\{4^1 \mod 11 = 4, 4^2 \mod 11 = 5, 4^3 \mod 11 = 9, 4^4 \mod 11 = 3, 4^5 \mod 11 = 1\} = \{1, 3, 4, 5, 9\}$ . The order of this subgroup is q = 5.

Determining the k-th power of g,  $h = g^k$ , which is called discrete exponentiation, is relatively easy to calculate. The inverse operation, to determine k for given h is a much more challenging task, which is known as the discrete logarithm problem (DLP). Obviously, it is essential to use groups that provide a DLP which is very hard to solve, while the exponentiation is easy to calculate.

Example: From our group  $\langle g \rangle$  let us take the exponent k = 3 and determine

$h = 4^3 \mod 11 = 9$ . The DLP in this case is to determine k for the equation  $9 = 4^k \mod 11$ . In this simple example it easy to try every possible power to find the solution. For large k > 100 bit this approach is obviously not feasible. Today, the best known method to calculate the discrete logarithm in subgroups is Pollard's rho algorithm [35]. The expected running time as function of the order of the subgroup q is proportional to

$$\sqrt{\frac{\pi q}{2}} \approx 1.25\sqrt{q}$$

Alternatively the Number Field Sieve (NFS) approach is applicable. This method solves the DLP for the complete based group  $\mathbb{G}$ . The expected running time of this algorithm is proportional to

$$e^{(1.9229+O(1))\cdot\ln(p)^{1/3}\cdot\ln(\ln(p))^{2/3}},$$

which is in contrast to Pollard's rho method subexponential in terms of the size of the parameter. But since the size p of the base group is much larger than the order q of the subgroup, the running time of both methods is roughly the same. Todays recommended key sizes are 1024 bit for p and 160 bit for q. It is interesting that the most of todays known attacks on the DLP are done applying the NFS. In practice it seems to be faster to attack the complete group  $\mathbb{G}$  than the subgroup  $\langle g \rangle$ .

Also the largest broken DLP which is known for a 130-decimal digit prime p was computed applying the NFS. According to [20] it took three weeks on a 1.15 GHz 16-processor HP AlphaServer GS1280 to break the 430 bit key.

#### El Gamal encryption

An application of the discrete logarithm approach is El Gamal public-key encryption scheme. It is used when Bob wants to send a message to Alice without using a shared key. The public key that was set up by Alice is ( $\mathbb{G}$ , g, q, h), where  $\mathbb{G}$  is the base group, g is the generator of the subgroup and q is the order of the subgroup. The fourth element h is a member of the subgroup and was determined by Alice by calculating  $h = g^x \mod p$ . The integer power x is the private key (x < q) which is chosen arbitrarily.

To encrypt a message m < p, Bob does the following

- selects a random integer (k < q)

- computes  $c_1 = g^k \mod p$

- computes  $c_2 = m \cdot h^k \mod p$

The encrypted message is  $(c_1, c_2)$ . To decrypt the message Alice

• computes  $m = c_2 \cdot c_1^{-x} \mod p$

Alice hereby obtains the decrypted message, since

$$c_2 \cdot c_1^{-x} = \frac{c_2}{c_1^x} = \frac{m \cdot h^k}{(g^k)^x} = \frac{m \cdot (g^x)^k}{(g^k)^x} = m \frac{g^{kx}}{g^{kx}} = m.$$

When Eve eavesdrops the public key and the encrypted message, her challenge is to determine the public key x to obtain the decrypted content. This x can be calculated by solving the discrete logarithm  $h = g^x \mod p$ . The variables g, h and p are part of the public key. This challenge is an example for the discrete logarithm problem.

#### 2.2.3. Elliptic curve cryptography

Generally speaking, ECC is nothing more than a special version of the discrete logarithm scheme.

The specialty lies in the underlying group. The elements of the elliptic group  $\mathbb{E}$  are not natural numbers but two-dimensional points with x and y coordinates. Every point (x, y) on the curve satisfies an equation such as

$$y^2 + xy = x^3 + x^2 + b, (2.1)$$

where b is a parameter defining the curve. The coordinates x and y are member of a finite field. The Equation 2.1 corresponds to the elliptic curve "B-233" as is recommended by the NIST [50]. Since not every EC implies cryptographic strengths, it is suggested to apply only such curves that have been analyzed and deemed to be secure.

To become more general, all ECs are defined by the so termed Weierstrass equation:

$$y^{2} + a_{1}xy + a_{3}y = x^{3} + a_{2}x^{2} + a_{4}x + a_{6}, \qquad (2.2)$$

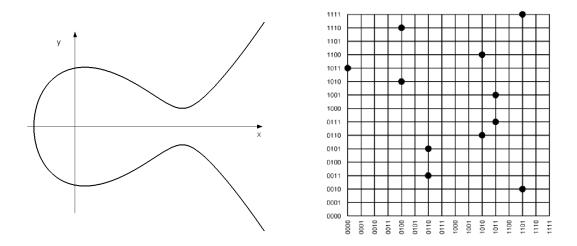

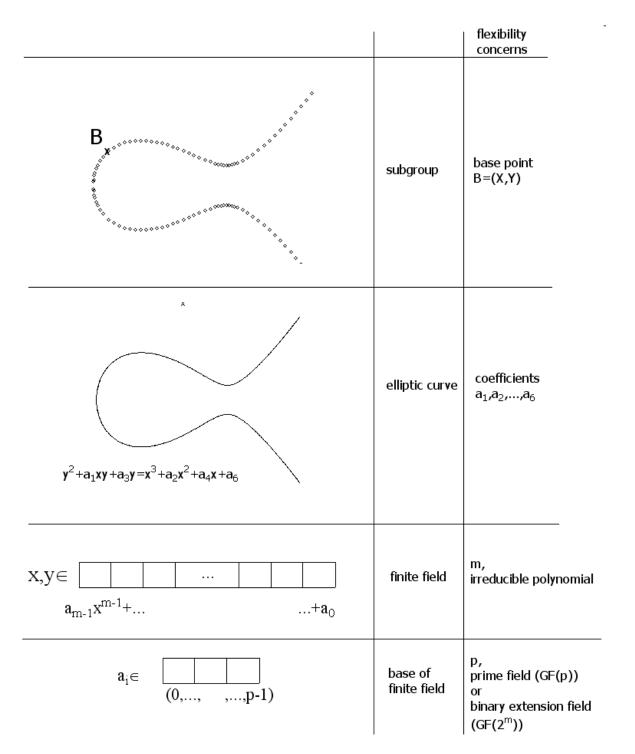

where  $a_1, ..., a_6$  and the coordinates of the points (x, y), which satisfy the equation, are elements of a base field  $\mathbb{B}$ . This field  $\mathbb{B}$  is not necessarily a finite field. Hence, also the field of real numbers  $\mathbb{R}$  is a conceivable base field for ECs. For cryptographic applications only finite fields are applied because of the issues that are connected with the required infinite accuracy of the decimals digits, which is not a problem in finite fields. In spite of this, also ECs based on  $\mathbb{R}$  are used in this thesis, in particular for presentation issues. Figure 2.3 shows an EC over  $\mathbb{R}$  and one over a small finite field. A geometrical representation of the curve and the operations, which are principally identical for all curves, is obviously much more meaningful for the  $\mathbb{R}$ -based curves.

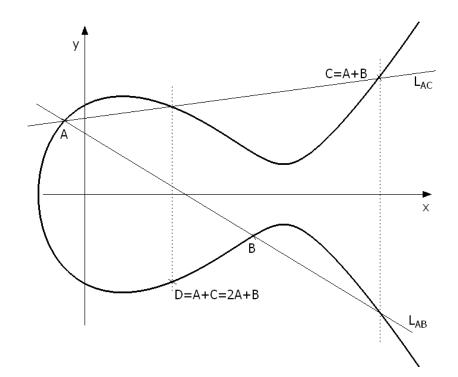

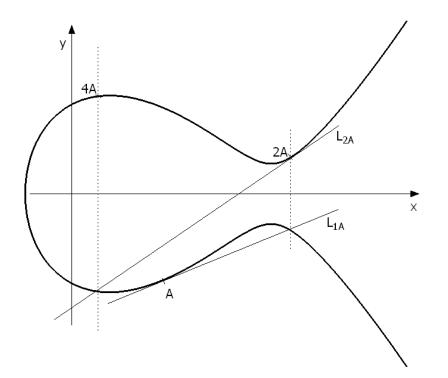

Independent of the applied elliptic equation and base field, all ECs satisfy the following properties, which are explained in order to understand the fundamental principles of ECC. An EC group is an additive finite Abelian group. This implies an additive operation is defined

Figure 2.3.: Exemplary elliptic curves based on real numbers on the left and based on the finite field  $GF(2^4)$  on the right. ECC is performed on finite fields. The typical 'EC-fish' is used for representation purposes.

in a way that every addition of two elements of  $\mathbb{E}$  results in another element of the group (C = A + B). The term 'Abelian' means the operation is commutativ. Furthermore, an identity 0 is defined as point at infinity. Since also for every point on the curve other than infinity an additive inverse (-A) is defined, subtraction is possible.

Having specified the addition of two points, one can define the result of repeated addition (Q = P + P + ... + P) as scalar multiplication of a point by an integer k  $(Q = k \cdot P)$ . One can create a subgroup of  $\mathbb{E}$ ,  $(\langle G \rangle, +)$ , with  $G \in \mathbb{E}$  and  $\langle G \rangle = \{i \cdot G : 0 \le i \le q-1\}$ , whereby the order q is the smallest nonzero integer such that  $q \cdot G = 0$ . This q is finite in ECs that are based on finite fields. The subgroup  $\langle G \rangle$  has similar attributes as the power operation based subgroup  $\langle g \rangle$ , which were described for the DLP. Analogous to the classic power operation, it is also very difficult to determine k for given  $Q \in \langle G \rangle$ , where  $Q = k \cdot G$ . This intractability of inverting scalar multiplication in  $\mathbb{E}$  is named the elliptic curve discrete logarithm (ECDL) problem. The properties of the ECDL allow to use it in the same way as the classic DL. The main difference consists in having an additive group  $(\mathbb{E},+)$  instead of the multiplicative group  $(\mathbb{G}, \cdot)$ . Furthermore, the application of the ECDL in cryptographic algorithms is very similar. The greatest benefit of EC become apparent when trying to solve the ECDL problem. Traditional DL can be broken with the subexponential number field sieve approach. This means, due to increasing computational power, the key sizes must grow very rapidely year by year and the keys become very long. For the ECDL problem, no equivalent of the NFS has been published. The best known way for attacking the ECDL is Pollard's rho method, which

*Table 2.2.:* Comparison of recommended future key sizes according to [2]. An implementation that should be used until today must already provide the corresponding degree of security today. DLP requires both field and key size to be secure.

| Year  | DLP   |     | RSA  | ECC | Hash size         |

|-------|-------|-----|------|-----|-------------------|

|       | field | key |      |     |                   |

| -2010 | 1024  | 160 | 1024 | 160 | SHA-1 (160 bit))  |

| -2030 | 2048  | 224 | 2048 | 224 | SHA-224 (224 bit) |

| >2030 | 3072  | 256 | 3072 | 256 | SHA-256 (256 bit) |

requires exponential operational effort. For EC the expected runtime as function of the order q of the subgroup is

$$\frac{\sqrt{\pi q}}{2} \approx 0.88\sqrt{q}.$$

Up to today no subexponential approach for EC has been reported. That is why a much shorter key length is adequate to provide a security level equivalent to RSA or traditional DL systems.

#### 2.2.4. Conclusions

The preceding sections demonstrate the need for public key approaches and introduce the most important algorithms. As indicator of the strength of these methods, a factor for the expected runtime for a successful attack was specified. Even though the equations show that, due to exponential effort, the keys of the ECC are the shortest at equal security strength, they do not provide information of the actual key lengths.

Based on the equations and the expected computational power reference [23] has determined lower bounds for computationally equivalent key sizes until the year 2050. An overview that corresponds to those results is provided in the recommendations by the NIST [2]. These recommendations for the minimum key lengths that are assumed to provide sufficient security over the time are shown in Table 2.2.

Until the year 2010, ECC key lengths of 160 bits are considered as secure, whereby the equivalent secure key length for the RSA method is 1024 bit. For security systems that should be applied until 2030, an ECC key length of 224 bit is recommended and for RSA, 2024 bit. This implies that a RSA system requires the tenfold key length to provide an equal security within the next 30 years.

Indeed, these results are estimates that do not consider breakthrough in cryptoanalytics or revolutionary cryptographic hardware, such as quantum computers. An example how fast the cryptoanlytic progress can weaken a cryptographic algorithm is the SHA-1 hash algorithm. The NIST recommendations from the year 2005 suggest SHA-1 as secure until the year 2010 but cryptgraphic progress has degraded the security strength of the algorithm so that already larger hash functions are recommended.

Despite the uncertainty concerning the concrete future key lengths and security strengths, Table 2.2 shows that the advantages of ECC compared to alternate public key approaches are significant.

# 3. Finite fields

Finite Fields are the basis of elliptic curve cryptography. The understanding of these fields is fundamental for efficient implementations of elliptic curves. This is why the fields and their operations are described in the following chapter. Hereby, based on previous research, different algorithms are specified and discussed. Additionally, feasible improvements are investigated to provide a basis for efficient hardware implementations. Special effort is spent on the polynomial multiplication operation. Improvements in this expensive operation, which have a significant impact on hardware designs, are described in this chapter.

### 3.1. Finite fields basics

Before starting with the actual operations, the basic kinds and properties of finite fields are introduced. Indeed, the fields and the algebraic background are not covered too exhaustively. For further readings [24] is recommended.

A finite field  $\mathbb{F}$  is a field that contains finitely many elements. In honor of Evariste Galois, these fields are also named Galois fields (*GF*). The number of elements in  $\mathbb{F}$  is called field order. The following operations are defined over elements of  $\mathbb{F}$ .

- Addition  $(\mathbb{F},+)$  as additive abelian group with identity 0

- Multiplication  $(\mathbb{F}\setminus\{0\},\cdot)$  as multiplicative abelian group with identity 1

Since distributive law also holds, every finite field is a commutative ring  $(\mathbb{F}, +, \cdot)$ . There are two main kinds of finite fields, prime fields GF(p) and extension fields  $GF(p^m)$ .

#### **3.1.1. Prime field** GF(p)

Prime fields GF(p) are finite fields with a prime number of elements p. The elements are usually denoted as a set of integers  $\{0, 1, 2, ..., p-2, p-1\}$ . The arithmetics in GF(p) are quite intuitive since they are performed with these natural integers.

Addition and subtraction is performed  $a + b \equiv (a + b) \mod p$ , which means the summation in the field is the remainder of the integer summation divided by p. Subtraction is expressed in terms of addition, while for a - b, a is added by the negative of b so that a - b = a + (-b)

- **Multiplication** is computed the same way as addition. The product in GF(p) is the remainder of the integer multiplication divided by p,  $a \cdot b \equiv (a \cdot b) \mod p$ .

- **Division** is more complicated, since it is not so obvious to find  $c = \frac{a}{b}$  so that  $c \cdot b = a$ . The most common way is to estimate the multiplicative inverse of the divisor  $b^{-1}$  $(1 = b \cdot b^{-1} \mod p)$  and multiply the dividend by it, so that  $c = a \cdot b^{-1}$ .

Prime fields are feasible base fields for ECC. There are also special elliptic curves based on prime fields that are recommended by the NIST [50]. Hardware implementations for these fields are presented in [44] and [33]. Despite that, prime fields are mainly used in other cryptographic methods than ECC. For example RSA relies on these fields.

Even though prime fields are not supposed to be implemented in hardware in this work, they will be used from time to time in this thesis, in particular for examples, due to their arithmetic, which is easier to comprehend than polynomial field arithmetic.

#### **3.1.2.** Extension fields $GF(p^m)$

Let p be a prime and m > 1.  $GF(p^m)$  is the field of equivalence classes of polynomials of degree at most m - 1 whose coefficients belong to GF(p). Then the elements of the field are:

$$GF(p^m) = \{a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \dots + a_2x^2 + a_1x + a_0 : a_i \in 0, 1, \dots, p-1\}.$$

One can imagine an element of this field as a number with m digits where every digit is number in the area 0..p - 1.

To provide the field operations, an extension field is constructed by finding an irreducible polynomial r(x) of degree m with coefficients in GF(p). Then  $GF(p^m) = GF(p)[x]/(r(x))$  is a finite field with the order  $p^m$ . This means the field  $GF(p^m)$  is the set of all equivalence classes of polynomials of x with coefficients out of GF(p) modulo r(x). This set contains exactly  $p^m$  equivalence classes and provides the additive and multiplicative operation.

Addition and subtraction is performed by standard polynomial addition and subtraction while coefficient arithmetic is done in GF(p).

$$a(x) + b(x) = (a_{m-1}x^{m-1} + \dots + a_1x + a_0) + (b_{m-1}x^{m-1} + \dots + b_1x + b_0)$$

=  $[(a_{m-1} + b_{m-1}) \mod p]x^{m-1} + \dots + [(a_1 + b_1) \mod p]x + [(a_0 + b_0) \mod p.]$

The subtraction process is analogous to the addition.

**Multiplication** in  $GF(p^m)$  is a multiple step operation. First, a standard polynomial multiplication is performed. The coefficient arithmetic in executed in GF(p). Since the result of the polynomial reduction is longer than m digits and hence is not fitting in the field, a second step is required. In this second step a reduction is performed. The result of this reduction is the remainder of the long product divided by the irreducible polynomial.

$a(x) \cdot b(x) = (a(x) \times b(x)) \mod r(x)$   $\times$ : polynomial multiplication r(x): irreducible polynomial

**Division** in  $GF(p^m)$  is a multiplication of the dividend with the inverse of the divisor. Determining the multiplicative inverse is a very complex operation that is usually solved by applying the 'extended Euclidean algorithm'.

Special subgroups of extension fields  $GF(p^m)$  are prime fields and binary extension fields. In these fields constantly m = 1 or p = 2, respectively. Even though extension fields that are not part of the two subgroups, are adequate for ECC, they are not relevant in practice. A practical application are 'optimal extension fields' [1]. These fields are fields such as  $GF((2^{61} - 5)^3)$  or  $GF((2^{32} - 5)^5)$ , which efficiently use the sizes of registers and operations of general purpose processors.

### **3.1.3.** Binary extension fields $GF(2^m)$

Binary finite fields are a special kind of extension fields with the prime characteristic p = 2. The elements of the groups are:

$$GF(2^m) = \{a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \dots + a_2x^2 + a_1x + a_0 : a_i \in \{0,1\}\}.$$

The elements can also be written as bit vector  $(a_{m-1}, a_{m-2}, ..., a_2, a_1, a_0)_2$ . It corresponds to the hardware and software representations, where the *m* binary values are stored in a bit array of the size *m*. As for the general extension fields, an irreducible polynomial r(x) is required to provide the field operations. This irreducible polynomial has the degree *m* and the coefficients are in GF(2). Then  $GF(2^m) = GF(2)[x]/(r(x))$  is a finite field with the order  $2^m$ .

Since the coefficients are delimited to zero or one, operations can be performed much easier. It can be seen in Table 3.1 that both addition and subtraction in GF(2) are equivalent to the XOR operation.

| a | b | addition (a+b) subtraction (a-b) |          |                               | XOR $(a \oplus b)$ |   |

|---|---|----------------------------------|----------|-------------------------------|--------------------|---|

|   |   | simple                           | $\mod 2$ | $1\ 2  \text{simple}  \mod 2$ |                    |   |

| 0 | 0 | 0                                | 0        | 0                             | 0                  | 0 |

| 0 | 1 | 1                                | 1        | -1                            | 1                  | 1 |

| 1 | 0 | 1                                | 1        | 1                             | 1                  | 1 |

| 1 | 1 | 2                                | 0        | 0                             | 0                  | 0 |

Table 3.1.: Addition and subtraction in GF(2) is equivalent to XOR

Addition and subtraction are performed by standard polynomial addition and subtraction. The coefficient arithmetic is done in GF(2) that can be substituted by simple XOR operations.

$$a(x) + b(x) = (a_{m-1}x^{m-1} + \dots + a_1x + a_0) + (b_{m-1}x^{m-1} + \dots + b_1x + b_0)$$

=  $[(a_{m-1} + b_{m-1}) \mod 2]x^{m-1} + \dots + [(a_1 + b_1) \mod 2]x + [(a_0 + b_0) \mod 2]$

=  $[(a_{m-1} \oplus b_{m-1})]x^{m-1} \oplus \dots \oplus [(a_1 \oplus b_1)]x + [(a_0 + b_0)]$

The subtraction is completely identical. When a(x) and b(x) are represented as m-bit bit arrays, addition and subtraction can be performed by a simple array-XOR:

$$a(x) + b(x) \equiv a(x) - b(x) \equiv b(x) - a(x) = a(x) \oplus b(x)$$

- **Multiplication** in  $GF(2^m)$  is the same two-step operation as in the extension fields. A polynomial multiplication is followed by a reduction step. The advantage of binary fields is again that both steps are taking profit from the faster XOR operation. Polynomial multiplication and reduction in  $GF(2^m)$  are investigated in detail later.

- **Division** in  $GF(2^m)$  traditionally is performed by multiplication with the inverse of the divisor. An approach that performs a division in one step has been introduced in [46].

All further elliptic curve research in this work is based on  $GF(2^m)$ , because properties of these fields are especially suited for hardware implementations. Major properties are:

- Addition and subtraction are XOR operations.

- No carries are required, which usually slow down large integer arithmetics.

- The binary character of the coefficients allows an efficient representation in hardware. For example, an element in  $GF(2^{163})$  can be stored in 163 flip flops.

Since elliptic curves on these fields have been standardized and analyzed for years, high level of experience and security has been attended. This provides a fundamental basis for special ECC hardware accelerators. In the following, multiplication, squaring as a special multiplication, reduction and the operation of finding the inverse in  $GF(2^m)$  are described and investigated. The addition operation is obvious, so that no further investigations are required.

## 3.2. Polynomial multiplication

Polynomial multiplication in  $GF(2^m)$  is a very expensive operation in the base field. Applying classic algorithms, the bit complexity of this operation is  $O(m^2)$ . This means, double bit length leads to quadruple complexity. For bit lengths of many hundred bits this is very crucial. Advanced algorithms obtain less complexity. In this section the classic method and variations of the faster Karatsuba multiplication are discussed. Finally, improved applications of the iterative Karatsuba approach are described and compared.

#### 3.2.1. Classic polynomial multiplication

The classic polynomial multiplication (CPM) is a straightforward translation of the classic school multiplication algorithm. Considering a multiplication of two polynomials A(x) and B(x), each of degree m, one obtains the product C(x) of the degree 2m - 1. The coefficients of C(x),  $c_{0}...c_{2m-2}$ , are determined in the following way: [11]

The estimation of the 2m-1 bit long product out of two m-1 bit inputs takes  $m^2$  partial one bit multiplications and  $(m-1)^2$  additions. Since in  $GF(2^m)$  one bit multiplications are AND operations and one bit additions are XOR operations,  $(m-1)^2$  XOR and  $m^2$  AND gates are required for the CPM.

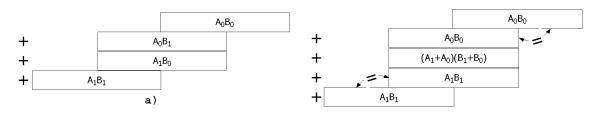

*Figure 3.1.:* Schematic comparison of classic polynomial method (a)) and Karatsuba multiplication (b)). CPM requires four partial multiplications and three accumulations while Karatsuba needs three different partial multiplications and four accumulation operations.

#### 3.2.2. Karatsuba multiplication

Karatsuba introduced in [21] a multiplication approach that decreases the complexity of the operation. Originally, the method was presented to reduce the number of partial multiplications for a decimal multiplication:

$$(a+b\cdot 10^n)(c+d\cdot 10^n) = ac + [(a+b)(c+d) - ac - bd]10^n + bd\cdot 10^{2n}$$

This means that splitting the decimal factors in two equally long parts and multiplying the partial factors with the special method reduces the number of partial multiplications to three. The approach can be easily adapted to polynomial multiplications in  $GF(2^m)$ :

$$(a+b\cdot x^{\frac{m}{2}})(c+d\cdot x^{\frac{m}{2}}) = ac + [(a+b)(c+d) + ac + bd]x^{\frac{n}{2}} + bd\cdot x^{m}$$

For a polynomial multiplication of  $A(x) \cdot B(x)$  where

$$A(x) = (a_{m-1}, a_{m-2}, ..., a_1, a_0)_2 = A_0 + A_1 \cdot x^{m/2}$$

$$A_0 = (a_{m-1}, a_{m-2}, ..., a_{m/2})_2 \text{ and } A_1 = (a_{m/2-1}, ..., a_1, a_0)_2$$

and corresponding B(x), one obtains

$$(A_0 + A_1 \cdot x^{\frac{m}{2}})(B_0 + B_1 \cdot x^{\frac{m}{2}}) = A_0B_0 + [(A_0 + A_1)(B_0 + B_1) + A_0B_0 + A_1B_1]x^{\frac{m}{2}} + A_1B_1 \cdot x^{\frac{m}{2}}$$

This operation compared to the classic multiplication is illustrated in Figure 3.1. It may be seen that an m-bit multiplication performed by the CPM corresponds to the accumulation of four partial m/2-bit multiplications. The alternative Karatsuba method requires the addition of five terms. But since two terms are duplicates, only three partial multiplications are required. Hence, Karatsuba takes more additions but less partial multiplications. We know that additions, especially in  $GF(2^m)$ , are cheap operations with linear complexity. In contrast multiplications are quite expensive. That is why the Karatsuba approach is an improvement concerning complexity.

The significant benefit of the method becomes apparent by applying it recursively. This means

the partial multiplications are split into smaller partial multiplications which are split again. This recursive approach reduces the bit complexity of a multiplication to  $O(m^{lg_23}) \approx O(m^{1.58})$ . For the determination of this complexity, one can recall the original formula:

$$a_1x^m + a_0 \cdot b_1x^m + b_0 = a_1b_1x^{2m} + [(a_0 + a_1)(b_0 + b_1) + a_1b_1 + a_0b_0]x^m + a_0b_0$$

This formula consists of three m-bit-multiplications, two m-bit-additions and four 2m-bit additions. Since addition operations entail linear complexity, one can simplify the number of accumulations to ten m-bit additions. Hence, one step requires three partial multiplications and ten addition. The recursively application of that approach leads to the following conclusions, depending on the recursion level (l):

| Data word size:                           | $s_l = 2 \cdot s_{l-1}; \ s_0 = 1$                    |

|-------------------------------------------|-------------------------------------------------------|

| Needed single bit multiplications (ANDs): | $n_l = 3 \cdot n_{l-1}; \ n_0 = 1$                    |

| Needed single bit additions (XORs):       | $x_l = 3 \cdot x_{l-1} + 10 \cdot s_{l-1}; \ x_0 = 0$ |

This means, when l = 0, the data word size is 1 bit, no addition is required, but one 1 bit multiplication, that is a single AND operation. At l = 1, 2-bit words are multiplied that apply three 1-bit multiplications and ten 1-bit additions. For l = 5 this sequence results in 32-bit multiplications that require 2110 XOR and 243 AND operations.

As next step the recursive sequence can be transferred into explicit formulas as function of l:

$$s_l = 2^l$$

$$n_l = 3^l$$

$$x_l = 10(3^l - 2^l)$$

(3.1)

The number of AND and XOR operations as function of the bit length m (corresponds to  $s_l$ ) of a data word can finally be expressed as:

Number of ANDs:

$$m^{\log_2 3} \approx m^{1.58}$$

(3.2)

Number of XORs:  $10 \cdot m^{\log_2 3} - 10m$

Since both complexities are  $O(m^{\log_2 3})$ , the total complexity of the classic Karatsuba method (CKM) is  $O(m^{\log_2 3})$ .

#### 3.2.3. Iterative Karatsuba multiplication

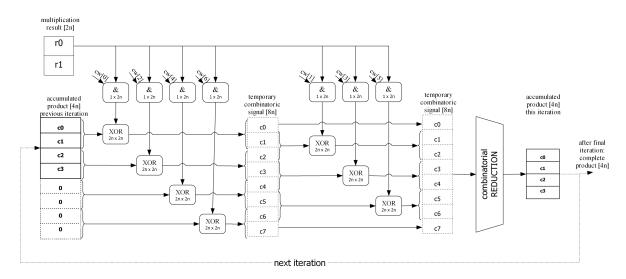

In [5] the Iterative-Karatsuba method (IKM) was introduced, which is an adaption of the original Karatsuba method. The IKM splits the operands into segments as in the CKM, but partial multiplications are processed iteratively. Instead of one monolith recursive

| <i>Table 5.2.</i> Accumulation table of the IKM [5]                                                        |          |            |          |                      |            |            |          |        |

|------------------------------------------------------------------------------------------------------------|----------|------------|----------|----------------------|------------|------------|----------|--------|

| Partial multiplication Accumulation                                                                        |          |            |          | $\operatorname{ons}$ |            |            |          |        |

| $[a_0 \cdot b_0][0]$                                                                                       |          | I I        | l        |                      | θ          | ιθ         | $\oplus$ | i ⊕    |

| $[a_0 \cdot b_0][1]$                                                                                       |          | I  <br>I   | l<br>I   | $\oplus$             | $ \oplus$  | $  \oplus$ | $\oplus$ | <br>   |

| $[a_1 \cdot b_1][0]$                                                                                       |          |            | l        | $\oplus$             | $\oplus$   | !⊕         | $\oplus$ | I      |

| $[a_1 \cdot b_1][1]$                                                                                       |          | I I        | $\oplus$ | $\oplus$             | ı ⊕        | ı ⊕        | l<br>I   | I      |

| $[a_2 \cdot b_2][0]$                                                                                       |          | I  <br>I   | $\oplus$ | $\oplus$             | $  \oplus$ | $  \oplus$ | l<br>I   | <br>   |

| $[a_2 \cdot b_2][1]$                                                                                       |          | $\oplus$   | $\oplus$ | $\oplus$             | $\oplus$   | I          | 1        | I      |

| $[a_3 \cdot b_3][0]$                                                                                       |          | $\oplus$   | $\oplus$ | $\oplus$             | $\oplus$   | I          | I<br>I   | I      |

| $[a_3 \cdot b_3][1]$                                                                                       | $\oplus$ | $ \oplus $ | $\oplus$ | $\oplus$             | <br>       | <br>       | <br>     | I<br>I |

| $[(a_0\oplus a_1)\cdot (b_0\oplus b_1)][0]$                                                                |          |            | I        |                      | $\oplus$   | I          | $\oplus$ | l      |

| $[(a_0\oplus a_1)\cdot (b_0\oplus b_1)][1]$                                                                |          | I I        | l        | $\oplus$             | I          | ¦⊕         | l        | I      |

| $[(a_0\oplus a_2)\cdot (b_0\oplus b_2)][0]$                                                                |          | I  <br>I   | l<br>I   |                      | $  \oplus$ | $  \oplus$ | <br>     | l<br>I |

| $[(a_0\oplus a_2)\cdot (b_0\oplus b_2)][1]$                                                                |          | I I        | l<br>I   | $\oplus$             | $ \oplus$  | l<br>I     | 1        | l<br>I |

| $[(a_1\oplus a_3)\cdot (b_1\oplus b_3)][0]$                                                                |          | I          | l        | $\oplus$             | ı ⊕        | l          | l        | I      |

| $[(a_1\oplus a_3)\cdot (b_1\oplus b_3)][1]$                                                                |          | I  <br>I   | $\oplus$ | $\oplus$             | <br>       | l<br>I     | l<br>I   | l<br>I |

| $[(a_2\oplus a_3)\cdot (b_2\oplus b_3)][0]$                                                                |          | I          | $\oplus$ |                      | $ \oplus$  | I<br>I     | 1        | I<br>I |

| $[(a_2\oplus a_3)\cdot (b_2\oplus b_3)][1]$                                                                |          | $\oplus$   | l        | $\oplus$             | 1          | 1          | 1        |        |

| $\boxed{[(a_0\oplus a_1\oplus a_2\oplus a_3)\cdot (b_0\oplus b_1\oplus b_2\oplus b_3)][0]}$                |          | <br>       | <br>     |                      | $\oplus$   | l<br>I     |          | <br>   |

| $\left[ (a_0 \oplus a_1 \oplus a_2 \oplus a_3) \cdot (b_0 \oplus b_1 \oplus b_2 \oplus b_3) ] [1] \right]$ |          |            | I<br>I   | $\oplus$             | I<br>I     | I<br>I     | l<br>I   | I<br>I |

|                                                                                                            | $c_7$    | $c_6$      | $c_5$    | $c_4$                | $c_3$      | $c_2$      | $c_1$    | $c_0$  |

Table 3.2.: Accumulation table of the IKM [5]

multiplication function, in that approach smaller multiplications are performed and the products are successively accumulated to the final result. It was also revealed that calculating the segments of the result separately can reduce the number of XOR operations.

Consider, the input words of the length m are split into four segments each. Then the product obtains eight segments of similar size m/4.

### $a_3a_2a_1a_0 \cdot b_3b_2b_1b_0 = c_7c_6c_5c_4c_3c_2c_1c_0$

For the beginning, this segmentation in four pieces is nothing else than a classic Karatsuba in the second recursion level. This is why Equations 3.2 can be applied to determine the number of partial multiplications and additions. Hence, one can expect nine partial multiplication and 50 partial additions.

All operations after the unrolling are depicted in Table 3.2. The first column is the partial multiplication. Since the products have the double size, each product is written twice: one for the lower ([0]) and one for the higher part ([1]). The right columns show for which segments of c the partial results are accumulated. For example

$$c_1 = a_0 \cdot b_0[1] \oplus a_1 \cdot b_1[0] \oplus a_1 \cdot b_1[1] \oplus (a_0 \oplus a_1) \cdot (b_0 \oplus b_1)[0].$$

Surprisingly, the number of XOR operations does not correspond to the estimations. Table 3.2 shows 10 XOR operations for the determination of the factors and 42 XOR operation for the accumulation of the partial products. These are 12 operations more than expected. The reason for the discrepancy is that due to the unrolling, some additions are executed twice. But it opens the possibility of reducing the number of XOR operations by reusing summations of already accumulated partial products. For example, the summation of  $a_0 \cdot b_0[1] \oplus a_1 \cdot b_1[0] \oplus a_1 \cdot b_1[1]$  can not only be used for  $c_1$  but for  $c_2$  and  $c_3$  as well. In [5] a chain of additions was presented that reduces the number of XOR operations in the accumulation process from 42 XORs as shown in Table 3.2 to 29 XOR operations when reusing previous partial results. Together with the 10 XORs in factor generation, this is already less than the 40 XORs of the CKM. Even though addition is a cheap operation, the reduction of these operations accelerates hardware and software implementations.

#### 3.2.4. Improvements of the iterative Karatsuba multiplication

Based on the IKM approach further improvements are discussed. First, an improved chain for the accumulation of the partial results  $c_0..c_8$  is presented. It could be observed that the accumulation of the partial results  $c_0..c_8$  as it was presented in [5] has left room for improvements. Trying other sequences, a chain could be found that only requires 24 XOR operations for the accumulation process. The corresponding sequence is depicted in Table 3.3. Together with the ten unchanged additions, which are necessary for the determination of the factors, 34 additions are required. These are six accumulations less than required for the CKM. The number of partial multiplications is unaffected.

Considering the partial multiplications are performed by the classic recursive Karatsuba method as it was described for the original IKM, the following complexities for the improved approach can be determined:

Number of ANDs:

$$9 \cdot \frac{m}{4}^{log_2 3} = m^{log_2 3} \approx m^{1.58}$$

Number of XORs:  $9 \cdot (8(\frac{m}{4})^{log_2 3} - 8\frac{m}{4}) + 34\frac{m}{4} = (10 \cdot m^{log_2 3} - 10m) - 4m$

With only 4m XOR operations less compared to the original Karatsuba method, the approach effects in a relatively small gain in performance. However, applied recursively, this small gain can make a significant difference. Consider that the partial multiplications are also performed by the improved IKM approach. Then the recursive function for the number of XOR operations as function of the recursion level l is:

$$x_l = 9x_{l-2} + \frac{34}{4}4^{l-2},$$

| Step | Partial product                                     | Sequence                                        |

|------|-----------------------------------------------------|-------------------------------------------------|

| 1    | $pr = a_0 \cdot b_0$                                | $c_0 = pr[0]$                                   |

|      |                                                     | $c_1 = pr[0] \oplus pr[1]$                      |

| 2    | $pr = a_3 \cdot b_3$                                | $c_7 = pr[1]$                                   |

|      |                                                     | $c_6 = pr[0] \oplus pr[1]$                      |

| 3    | $pr = a_1 \cdot b_1$                                | $c_1 = c_1 \oplus pr[0]$                        |

|      |                                                     | $c_5 = pr[1]$                                   |

| 4    | $pr = a_2 \cdot b_2$                                | $c_5 = c_5 \oplus pr[0]$                        |

|      |                                                     | $c_6 = c_6 \oplus pr[1]$                        |

| 5    | $pr = (a_0 \oplus a_1) \cdot (b_0 \oplus b_1)$      | $c_2 = c_1 \oplus c_5 \oplus pr[1]$             |

|      |                                                     | $c_1 = c_1 \oplus pr[0]$                        |

|      |                                                     | $c_5 = c_5 \oplus c_6$                          |

| 6    | $pr = (a_2 \oplus a_3) \cdot (b_2 \oplus b_3)$      | $c_5 = c_5 \oplus pr[0]$                        |

|      |                                                     | $c_6 = c_6 \oplus pr[1]$                        |

| 7    | $pr = (a_1 \oplus a_3) \cdot (b_1 \oplus b_3)$      | $c_3 = c_1 \oplus c_5$                          |

|      |                                                     | $c_4 = pr[1] \oplus c_2 \oplus c_0$             |

|      |                                                     | $c_5 = c_5 \oplus pr[1]$                        |

|      |                                                     | temp = pr[0]                                    |

| 8    | $pr = (a_0 \oplus a_2) \cdot (b_0 \oplus b_2)$      | $temp = temp \oplus pr[1]$                      |

|      |                                                     | $c_2 = c_2 \oplus pr[0]$                        |

|      |                                                     | $c_3 = c_3 \oplus temp \oplus c_7 \oplus pr[0]$ |

|      |                                                     | $c_4 = c_4 \oplus temp \oplus c_6$              |

| 9    | $pr = ((a_0 \oplus a_1) \oplus (a_2 \oplus a_3))$ . | $c_3 = c_3 \oplus pr[0]$                        |

|      | $((b_0\oplus b_1)\oplus (b_2\oplus b_3))$           | $c_4 = c_4 \oplus pr[1]$                        |

Table 3.3.: This improved operation sequence reduces the number of XOR operation for the accumulation in IKM to 24.

which is rewritten as explicit function of the factor length:

$$x_n = \frac{34}{5}m^{\log_2 3} - \frac{34}{5}m. \tag{3.3}$$

This implies that the 'Recursively Applied Iterative Karatsuba' (RAIK) results in a reduction of the XOR operations of 18% compared to classic Karatsuba. The number of AND operations is not affected.

| Bit length | CPM    | CKM    | IKM    | RAIK   |

|------------|--------|--------|--------|--------|

| 4          | 9      | 50     | 34     | 34     |

| 8          | 49     | 190    | 158    | 129    |

| 16         | 225    | 650    | 586    | 442    |

| 32         | 961    | 2110   | 1982   | 1435   |

| 64         | 3969   | 6650   | 6394   | 4522   |

| 128        | 16129  | 20590  | 20078  | 14001  |

| 256        | 65025  | 63050  | 62026  | 42874  |

| 512        | 261121 | 191710 | 189662 | 130363 |

Table 3.4.: Number of one bit XOR operations for different factor bit lengths and with different multiplication methods

Table 3.5.: Number of one bit AND operations for different factor bit lengths and with different multiplication methods

| Bit length | CPM    | CKM   | IKM   | RAIK  |

|------------|--------|-------|-------|-------|

| 4          | 16     | 9     | 9     | 9     |

| 8          | 64     | 27    | 27    | 27    |

| 16         | 256    | 81    | 81    | 81    |

| 32         | 1024   | 243   | 243   | 243   |

| 64         | 4096   | 729   | 729   | 729   |

| 128        | 16384  | 2187  | 2187  | 2187  |

| 256        | 65536  | 6561  | 6561  | 6561  |

| 512        | 262144 | 19683 | 19683 | 19683 |

#### 3.2.5. Comparison

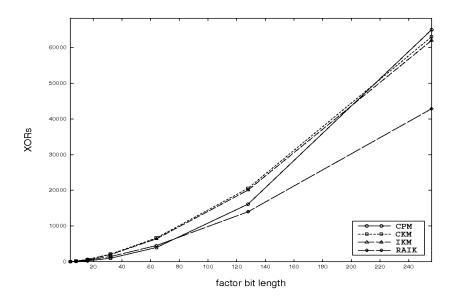

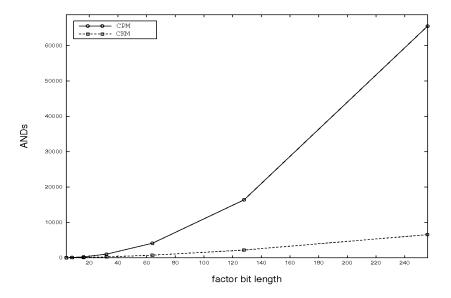

Having described different methods for multiplying polynomials in  $GF(2^m)$ , these approaches should be compared by the total number of operations for possible factor lengths. The considered multiplication methods are the classic polynomial multiplication (CPM), the classic Karatsuba multiplication (CKM), the iterative Karatuba multiplication (IKM), and the recursively applied iterative Karatsuba (RAIK) multiplication. The formulas for the determination of the complexity of AND and XOR operations are presented in the previous sections.

Table 3.4 and Table 3.5 provide a comparison of the methods that have been discussed so far, concerning the number of single bit XOR and single bit AND operations respectively. The graphical representation of the tables is also shown in Figures 3.2 and 3.3.

All Karatsuba based multiplications obtain the same number of AND operations. This number is always lower compared to CPM and the slope is also much slower. For the XOR operations the results are much more interesting. It is noticeable that for small factor lengths CPM requires the least number of operations. But this method is also the one that increases fastest. The slowest increment of operations is obtained by the RAIK method. Hence, it is the optimal

Figure 3.2.: Graphical representation of Table 3.4. The classic Karatsuba methods and CPM need a similar number of XOR operations for a multiplication. RAIK, the improved Karatsuba approach, needs 32% less XORs.

Figure 3.3.: Graphical representation of Table 3.5. The number of AND operations is significantly less for the Karatsuba approach than for CPM.

| Bit length | CPM   | CKM   | RAIK  | combined | combined |

|------------|-------|-------|-------|----------|----------|

|            |       |       |       | CKM/CPM  | RAIK/CPM |

| 4          | 9     | 50    | 34    | 9        | 9        |

| 8          | 49    | 190   | 129   | 49       | 49       |

| 16         | 225   | 650   | 442   | 227      | 217      |

| 32         | 961   | 2110  | 1435  | 841      | 713      |

| 64         | 3969  | 6650  | 4522  | 2843     | 2497     |

| 128        | 16129 | 20590 | 14001 | 9169     | 7505     |

| 256        | 65025 | 63050 | 42874 | 28787    | 24649    |

Table 3.6.: Number of one bit XOR operations for different factor bit lengths and with different multiplication methods

Table 3.7.: Number of one bit AND operations for different factor bit lengths and with different multiplication methods

| Bit length | CPM   | CKM  | RAIK | combined | combined |

|------------|-------|------|------|----------|----------|

|            |       |      |      | CKM/CPM  | RAIK/CPM |

| 4          | 16    | 9    | 9    | 16       | 16       |

| 8          | 64    | 27   | 27   | 64       | 64       |

| 16         | 81    | 81   | 144  | 144      | 192      |

| 32         | 1024  | 243  | 243  | 576      | 576      |

| 64         | 4096  | 729  | 729  | 1296     | 1728     |

| 128        | 16384 | 2187 | 2187 | 5184     | 5184     |

| 256        | 65536 | 6561 | 6561 | 11664    | 15552    |

method for larger factor lengths.

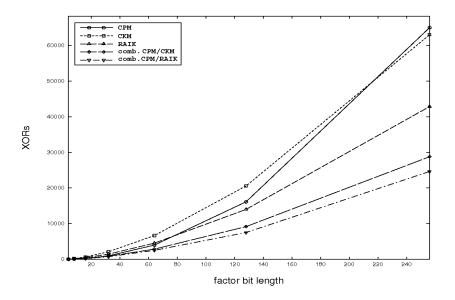

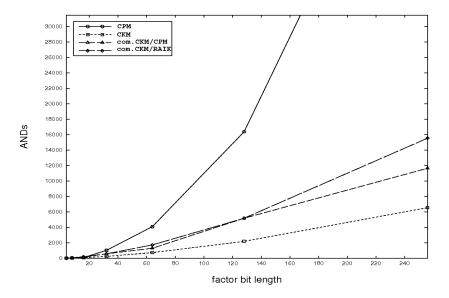

The fact that for small factor lengths the fewest XOR operations are obtained by the CPM, raises the idea of substituting deep recursion levels of the Karatsuba multiplications with CPM. For example with RAIK, a 64-bit multiplier uses 16-bit partial multipliers which use 4-bit partial multipliers. Following the Karatsuba method, the next step would apply 34 single bit XORs and 9 single bit ANDs for the calculation of the 4-bit partial multiplication. The CPM only requires 9 XORs and 16 ANDs. This means, using the CPM for the 4-bit partial multiplication instead of RAIK reduces the total number of operations from 43 to 25. Since the small partial multipliers are the base elements of every Karatsuba multiplier, the impact of this substitution is significant. The concrete numbers of XOR and AND operations using this combined approach are represented in Table 3.6 and 3.7. The numbers are estimated by applying the recursive formulas that were presented in the previous sections. The combined method for both two-segment-Karatsuba and four-segment-Karatsuba are depicted.

As expected, the number of XOR operation is reduced by the combined method. For a 256-bit RAIK multiplier the decrease is 43% from 42878 to 24649 XOR operations. In contrast, the number of AND operations is rising. For the 256-bit-example by 77% from 6561 to 11664

*Figure 3.4.:* Graphical representation of Table 3.6. The combined approaches require the least number of XOR operations, the classic approaches the most.

*Figure 3.5.:* Graphical representation of Table 3.7. The classic Karatsuba multiplication requires the least AND operations. The combined methods need more ANDs than the CKM, but much less than the CPM.

AND operations. Eventually, there are about 5000 AND operations more to compute but about 18000 XOR operations less. Effectively, that results in a reduction of 13000 total operations.

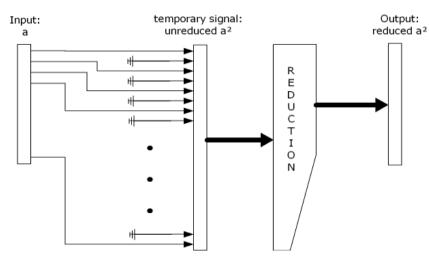

## 3.3. Polynomial squaring

Polynomial squaring in  $GF(2^m)$  can be done with standard polynomial multiplication as described in Section 3.2, as it is obvious that  $c(x) = a(x)^2 = a(x) \cdot a(x)$ . But applying special properties of the  $GF(2^m)$  can lead to implementations with much less complexity compared to standard multiplication.

In the most known GF(2) implementations (e.g. [43]) the following expression is used:

$$c(x) = a(x)a(x) = \sum_{i=0}^{m-1} a_i x^i \cdot \sum_{i=0}^{m-1} a_i x^i = \sum_{i=0}^{m-1} a_i x^{2i}$$

(3.4)

This expression is valid, since the finite fields  $GF(2^m)$  are commutative rings with prime characteristic p = 2. [24] proved that for every commutative ring with prime characteristic p it is true that  $(a + b)^p = a^p + b^p$ . They applied the properties of binomial coefficients. Since

$$\begin{pmatrix} p\\i \end{pmatrix} = \frac{p!}{i!(p-i)!} = p \frac{(p-1)!}{i!(p-i)!} \equiv 0 \mod p$$

it follows that

$$(a+b)^p = a^p + \binom{p}{1}a^{p-1}b + \dots + \binom{p}{p-1}ab^{p-1} + b^p = a^p + b^p$$

And since p = 2 for  $GF(2^m)$  Formula 3.4 is valid.

One can rewrite the coherence from Formula 3.4 to

$$(a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \dots + a_1x^1 + a_0x^0)^2 = a_{m-2}x^{2(m-2)} + a_{m-1}x^{2(m-1)} + \dots + a_1x^2 + a_0x^0$$

and see what actually happens. Every bit  $a_i$  from the input word at position i is moved to position 2i in the square. The other bits are filled with zeros. With other words, a 0-bit is inserted between every input bit. The complexity is O(m) because it is simply a reassignment of the bits.

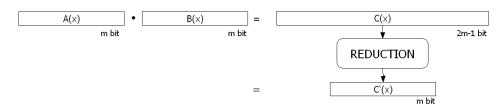

Figure 3.6.: Principle of the reduction operation: after a multiplication of two m bit polynomials, the result C(x) is too long. It must be reduced to an equivalent inside the field.

## 3.4. Reduction

Both polynomial multiplication and polynomial squaring result in data words that have a higher degree than the maximum field degree. To make them fit in the field, they have to be reduced. The fundamental scheme can be seen in Figure 3.6. The multiplication of two m bit data words results in a 2m - 1 bit product C(x). The process of determining the equivalent element in the field is termed reduction. The operation corresponds to the modulo operation in prime fields. That is why the classic reduction method in  $GF(2^m)$  is to divide the C(x) by the irreducible. The remainder of this division is the reduced product C'(x). There are also other methods for the reduction process that do not require a complete division. The multiplicative reduction and a fast reduction that has linear complexity are described in this section.

## 3.4.1. Polynomial division

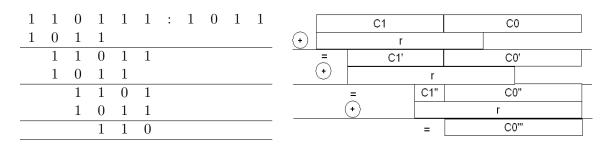

The first obvious solution for the reduction problem, is to perform a standard polynomial division in order to estimate the remainder. The polynomial division based reduction is shown as Algorithm 3.1, and an example is shown in Figure 3.7.

```

Algorithm 3.1: Polynomial division as reduction implementation

input : c(x), m = degree(field), r(x)

output: reduced polynomial = c(x) \mod r(x)

1 for i = degree(c) downto m do

2 if c_i = 1 then

3 c(x) \leftarrow c(x) \operatorname{XOR} r(x) \cdot x^{i-m};

4 end

5 end

6 return (c(x))

```

The algorithm does not compute the quotient but the remainder that eventually is the reduced value. In this algorithm every overlapping bit is reduced successively from left to right. Thus, the maximum number of iterations of the inner loop is deg(a) - deg(r) + 1. After a multiplication of two m bit words, the product has a bit length of 2m - 1. Then 2m - 1 - m + 1 = m iterations

#### CHAPTER 3. FINITE FIELDS

Figure 3.7.: Example of a simple polynomial reduction using polynomial division to compute the remainder.

of the inner loop must be performed in maximum. Since each of the possible m iterations is connected with a m bit XOR operation, the total effort of this method is  $O(m^2)$ .

## 3.4.2. Multiplicative reduction

The multiplicative reduction is the second possible reduction method. Hereby, repeatedly the product of the overlapping part C1(x) of C(x) and the reduction polynomial r(x) is subtracted from C(x). 'Overlapping' are the bits of C(x) on higher positions than the field degree. In Figure 3.7 and 3.8 overlapping part is C1, and C0 are the bits that are within the field boundaries. Since deg(C0(x)) = m, the coherence between C, C0, C1 can be written as

$$C(x) = C1(x)x^m + C0(x).$$

The multiplicative reduction is shown as Algorithm 3.2 and represented in Figure 3.8. By this, with every iteration at least the highest bit is reduced. This is working, because in finite fields the following property holds true:

$$C(x) \equiv C(x) - i \cdot r(x) \mod r(x)$$

for every *i*, and hence, also

$$C(x) \equiv C(x) - C1(x) \cdot r(x).$$

(3.5)

This shows that the result of the subtraction of the product of the irreducible polynomial and

Algorithm 3.2: Multiplicative reduction input : a(x), m = degree(a), r(x)output: reduced polynomial  $a(x) \mod c(x)$ 1  $C1(x) \leftarrow C(x)/x^m$ ; 2 while C1(x) <> 0 do 3  $C(x) \leftarrow C(x)$  XOR  $[C1(x) \cdot r(x)]$ ; 4  $C1(x) \leftarrow C(x)/x^m$ ; 5 end 6 return (C(x))

| 1  1  0  1  1  1  1  1  0  1  1 | C   | 21  | C0      |

|---------------------------------|-----|-----|---------|

| 1  1  1  1  0  1  0             | •   | C   | l · r   |

| 1 + 1 = 0 = 1                   | =   | C1' | C0'     |

| $1 \downarrow 0 1 1$            | (+) |     | C1' · r |

| 1 1 0                           |     | =   | C0"     |

*Figure 3.8.:* Simple example for multiplicative reduction. Exploiting the special properties of NIST irreducible polynomials, the number of steps is always limited to two.

the overlapping part from C(x) is still equivalent to C(x) in the finite field. And since

$$C(x) = C1(x)x^m + C0(x)$$

, and

$r(x) = x^m + r_{m-1}x^{m-1} + \dots + r_0$

(3.6)

it follows that

$$C(x) \equiv C(x) - C1(x) \cdot r(x)$$

$$\equiv [C1(x)x^{m} + C0(x)] - [C1(x) \cdot (x^{m} + r_{m-1}x^{m-1} + \dots + r_{0})]$$

$$\equiv [C1(x)x^{m} + C0(x)] - [C1(x)x^{m} + C1(x) \cdot (r_{m-1}x^{m-1} + \dots + r_{0})]$$

$$\equiv C0 - C1(x) \cdot (r_{m-1}x^{m-1} + \dots + r_{0})$$

$$\equiv C1(x) \cdot r_{m-1}x^{m-1} + \dots + C1(x) \cdot r_{0} + C0(x)$$

(3.7)

This implies that C1(x) is not multiplied by  $x^m$  anymore but by  $x^{m-1}$  in maximum. This way a new polynomial C'(x) can be defined:

$$C'(x) = C1(x) \cdot r_{m-1}x^{m-1} + \dots + C1(x) \cdot r_0 + C0(x)$$

which has a smaller degree than C(x). This C'(x) can be expressed as

$$C'(x) = C1'(x)x^m + C0'(x)$$

where deg(C0'(x)) = m - 1 and deg(C1'(x)) < deg(C1(x)). This simplified representation shows that in every multiplicative step at least one bit is reduced. When only one bit is cut in each iteration, still m - 1 steps are required. The m - 1 multiplications of factor size m result in a complexity of  $O(m \cdot m^{\log_2 3})$ , which is more expensive than reduction by division.

But taking a look to commonly used reduction polynomials reveals an interesting feature. As the five irreducible polynomials for the ECs recommended by the NIST (see Table 3.8) all reduction polynomials are either trinomials (three coefficients set) or pentanomials (five coefficients). This simplifies the multiplication remarkably. For example the multiplication

| Recommended field | reduction polynomial $r(x)$        |

|-------------------|------------------------------------|

| B-163             | $x^{163} + x^7 + x^6 + x^3 + 1$    |

| B-233             | $x^{233} + x^{74} + 1$             |

| B-283             | $x^{283} + x^{12} + x^7 + x^5 + 1$ |

| B-409             | $x^{409} + x^{87} + 1$             |

| B-571             | $x^{571} + x^{10} + x^5 + x^2 + 1$ |

Table 3.8.: Reduction polynomials from NIST elliptic curves [50]

of the overlapping part (C1(x)) with the trinomial  $x^{233} + x^{74} + 1$  is done by performing  $C1(x) + C1(x)x^{74} + C1(x)x^{233}$ . Efficient implementations can realize this operation with only two shifts and two XOR-operations. At least a full multiplier is not required.

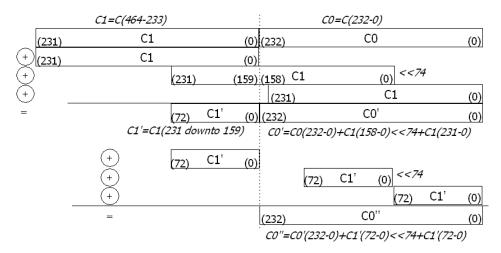

The commonly used reduction polynomials have another property which is very beneficial. The second highest coefficient set in the polynomial in a field  $GF(2^m)$  is always smaller than m/2. When substituting the coefficients of the reduction polynomial in Equation 3.7 according to this fact, it follows that a single iteration reduces more than m/2 bit of C1(x). Thus, after two steps C(x) is completely reduced.

This brings complexity of the multiplicative reduction down to two multiplications. The multiplications can be substituted by few shifts and XOR-operations. This is why the total complexity for the reduction in commonly used fields is O(m).

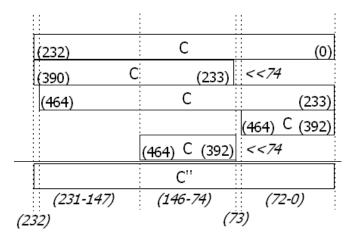

## 3.4.3. Fast reduction

The fast reduction is a special application of the multiplicative reduction for known reduction polynomials. The idea is, when the reduction polynomial is known, at design time a chain of XOR operations can be build that performs the reduction within one step as a direct mapping of the long input word.